我們在探個路一下 講講接下來可能會用到的東西

我用個 PPT 畫個圖

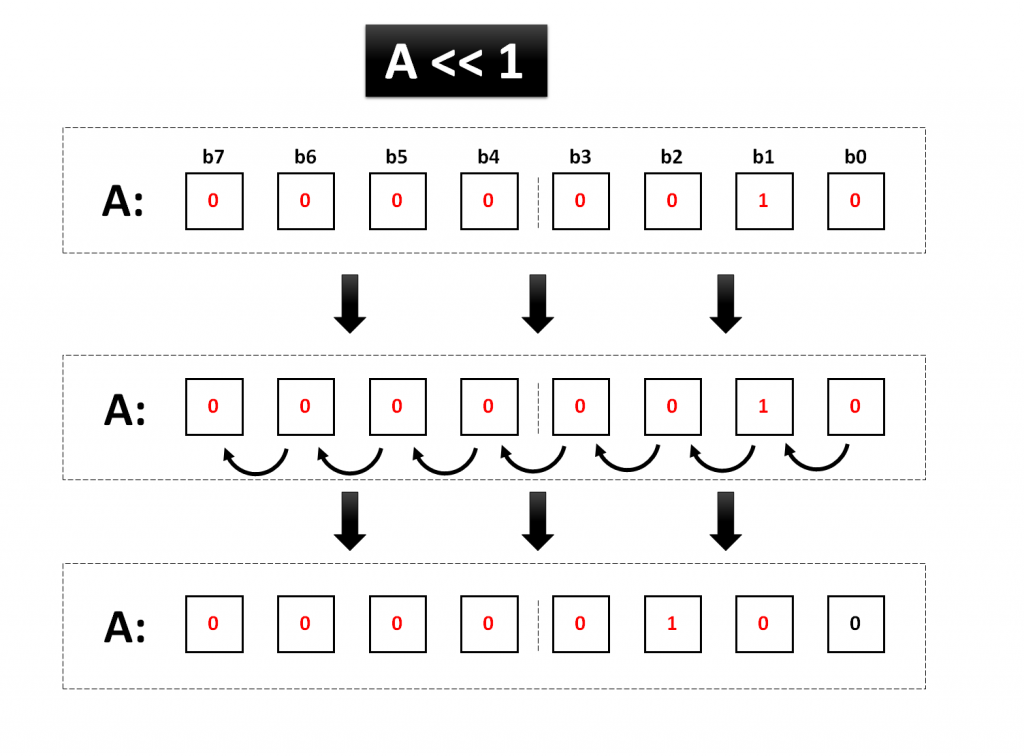

assign out1 = A << 1 ;

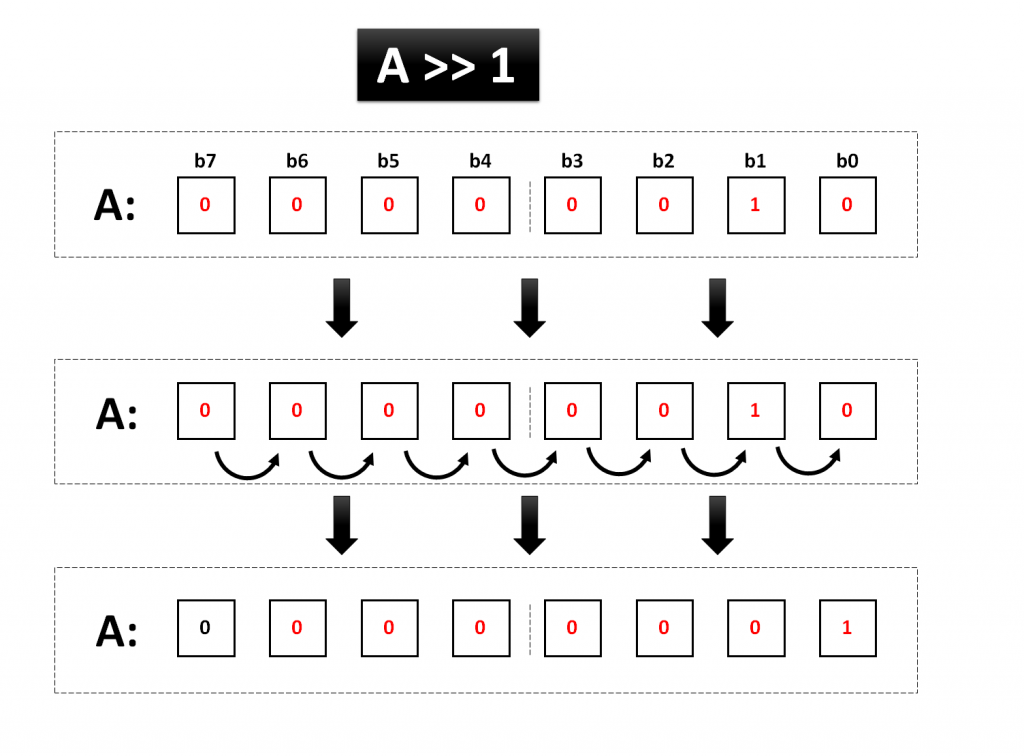

assign out1 = A >> 1 ;

我們來寫一個

隨著時間軸往左推 0001 → 0010 → 0100 → 1000

然後再推回來 1000 → 0100 → 0010 → 0001

第 1 步

來最初老樣子 有reg 初始化 always + case

module Clk_Add2(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Out1<=1;

end

else begin

case ()

1:

0:

default:

Out1<=0;

endcase

end

end

endmodule

第 2 步

接下來寫一個 Reg (Data) 來檢查 Out1有沒有到 1000 或是 0001

寫一個 reg Data;

馬上初始化 Data;

module Clk_Add2(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

// 寫一個 reg Data;

reg Date;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Out1<=1;

// 馬上初始化 Data;

Date <= 0;

end

else begin

case (Date)

1:

// 檢查 Out1有沒有到 1000 或是 0001

if(Out1==1) begin

end

else begin

end

0:

// 檢查 Out1有沒有到 1000 或是 0001

if(Out1==8) begin

end

else begin

end

default:

Out1<=0;

endcase

end

end

endmodule

第 3 步

填一下 位元移位

module Clk_Add2(reset1,clk,Out1);

input reset1 ,clk;

output[7:0] Out1;

reg[7:0] Out1;

reg Date;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Out1<=1;

Date <= 0;

end

else begin

case (Date)

1:

if(Out1==1) begin

//填一下 位元移位

Date <= 0;

Out1 <= Out1<<1;

end

else begin

//填一下 位元移位

Out1 <= Out1>>1;

end

0:

if(Out1==8) begin

//填一下 位元移位

Date <= 1;

Out1 <= Out1>>1;

end

else begin

//填一下 位元移位

Out1 <= Out1<<1;

end

default:

Out1<=0;

endcase

end

end

endmodule

第 4 步

tb 我就不解釋了

module tb1();

reg reset1 ,clk;

wire[7:0] Out1;

Clk_Add2 Test1(.reset1(reset1),.clk(clk),.Out1(Out1));

initial begin

clk<=0;reset1<=0;

#7 reset1<=1;

#6000 $stop;

end

always #5 clk<=~clk;

endmodule

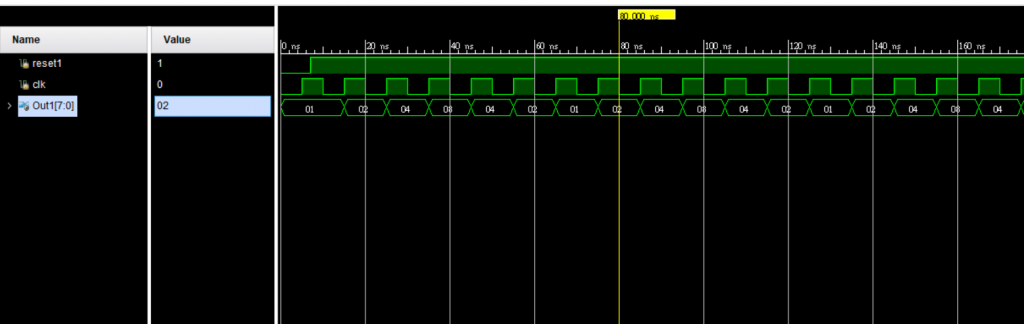

第 5 步

看看結果吧

明天我們再來畫這張圖長怎樣